Serial Adder Moore Model Verilog

The serial adder is a digital circuit in which bits are added a pair at a time.

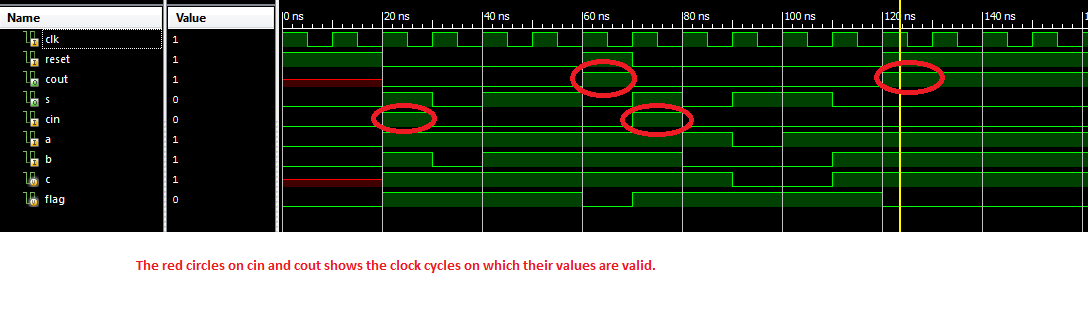

Let A and B be two unsigned numbers to be added to produce Sum = A + B. In this we are using three shift registers which are used to hold A, B and Sum. Now in each clock cycle, a pair of bits is added by the adder FSM and at the end of the cycle, the resulting sum is shifted into the Sum register.

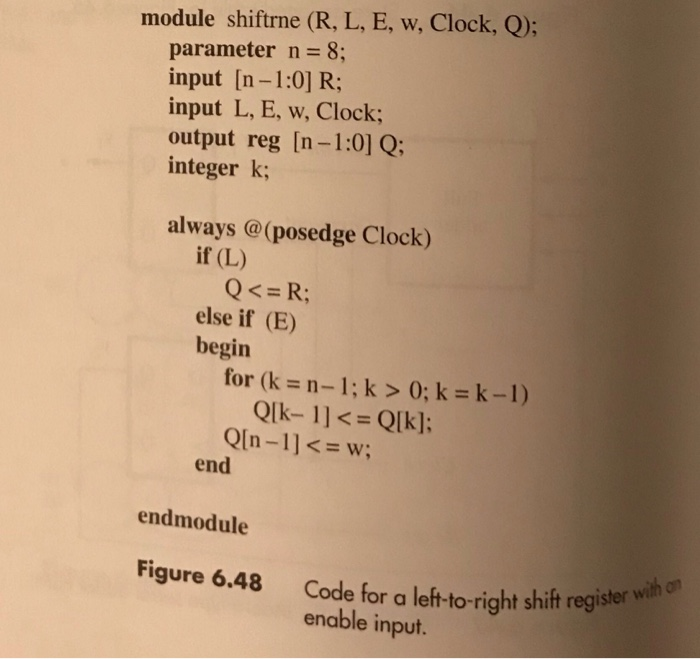

Design a serial adder circuit using Verilog. The circuit should add two 8-bit numbers, A and B. The result should be stored back into the A register. Use the diagram below to guide you. Hint: Write one module to describe the datapath and a second module to describe the control. Serial input of addends (inA, inB), LSB first. Serial generation of sum bits, LSB first (sum) Enable signal (en) to start computation. Done signal (done) on last computation (MSB of sum) Latch final sum bit until next execution. 4-bit serial adder operation. Design is a serial adder. It takes 8-bit inputs A and B and adds them in a serial fashion when the goinput is set to 1. The result of the operation is stored in a 9-bit sum register, The block diagram is attached. I am using Quartus II 13.0sp1 (64-bit) Web Edition. Only want to invest in a single N-bit adder, we can build a sequential circuit that processes a single subtraction at a time and then cycle the circuit N times. This circuit works on unsigned operands; for signed operands one can remember the signs, make operands positive, then correct sign of result. P A B-S N+1 N+1 N+1 Init: P 0, load A and B.

Mealy type FSM for serial adder:

Let G and H denote the states where the carry-in-values are 0 and 1. Output value s depends on both the state and the present value of inputs a and b.

In state G and H:

| Input valuation | Output (s) | State |

|---|---|---|

| 00 | 0 | FSM will remain in same state G |

| 01,10 | 1 | FSM will remain in same state G |

| 11 | 0 | FSM moves to state H |

| 01,10 | 0 | FSM will remain in same state H |

| 11 | 1 | FSM will remain in same state H |

| 00 | 1 | FSM moves to state G |

A single Flip-Flop is needed to represent the two states. The next state and output equations are:

Y = ab + ay + by

s = a ⊕ b ⊕ y

N Bit Adder Verilog

The flip-flop can be cleared by the Reset signal at the start of the addition operation.

Full Adder Verilog Code

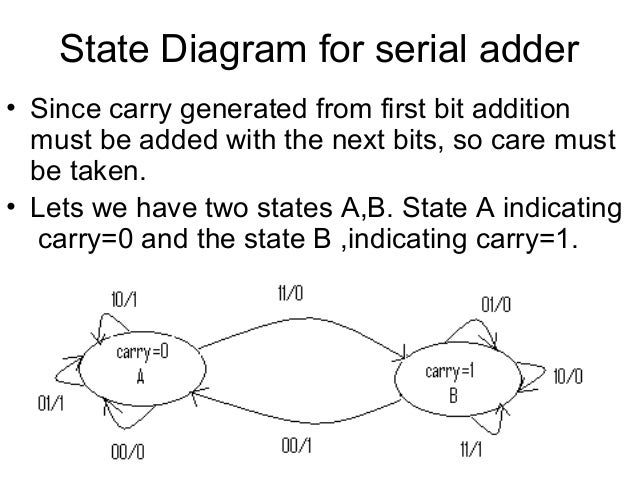

Moore type FSM for serial adder:

In a Moore type FSM, output depends only on the present state. Since in both states, G and H, it is possible to produce two different outputs depending on the valuations of the inputs a and b, a Moore type FSM will need more than two states. Therefore we will four states namely: G0, G1, H0 and H1.

The next state and output equations are:

Y1 = a ⊕ b ⊕ y2

Half Adder Verilog Code

Y2 = ab + by2 + by2

s = y1

The only difference between circuits of Mealy and Moore type FSM for serial adder is that in Moore type FSM circuit, output signal s is passed through an extra flip-flop and thus delayed by one clock cycle with respect to the Mealy type FSM circuit.

1 Bit Full Adder Verilog

References: Fundamentals of Digital Logic with VHDL Design